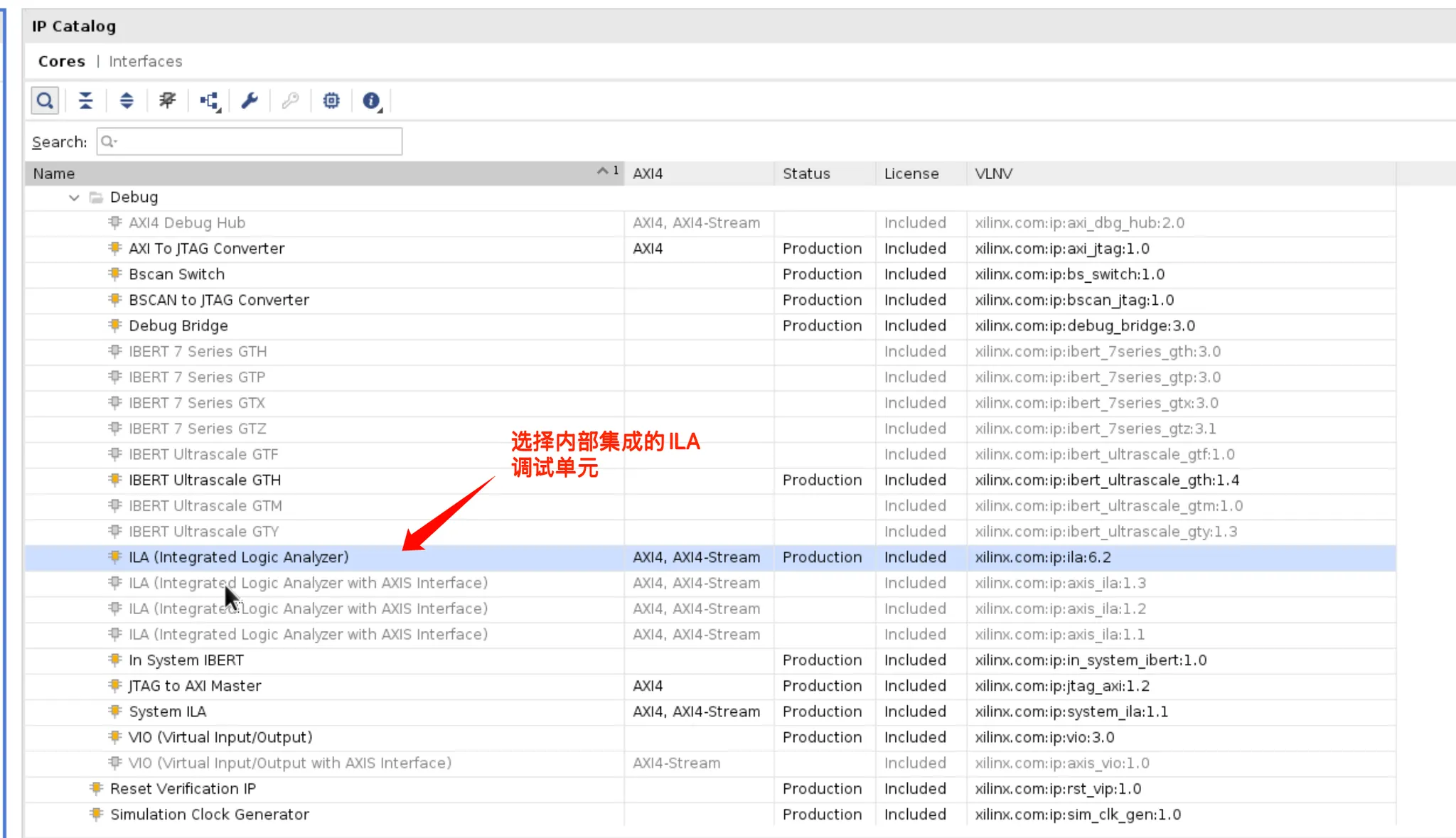

FPGA中如何使用内嵌逻辑分析仪

在 FPGA 调试中,很多问题无法通过仿真复现,例如时序相关 Bug、跨时钟域问题、上板后异常行为等。这时,内嵌逻辑分析仪(ILA, Integrated Logic Analyzer)是最有效的调试手段之一。

本文简要介绍 FPGA 中 ILA 的使用方法和工程要点。FPGA的开发流程采用Synplify+Vivado流程实现。

什么是 ILA?

ILA 是集成在 FPGA 内部的逻辑分析仪,能够:

- 在真实运行环境下采样内部信号

- 通过 JTAG 将采样数据回传到 PC

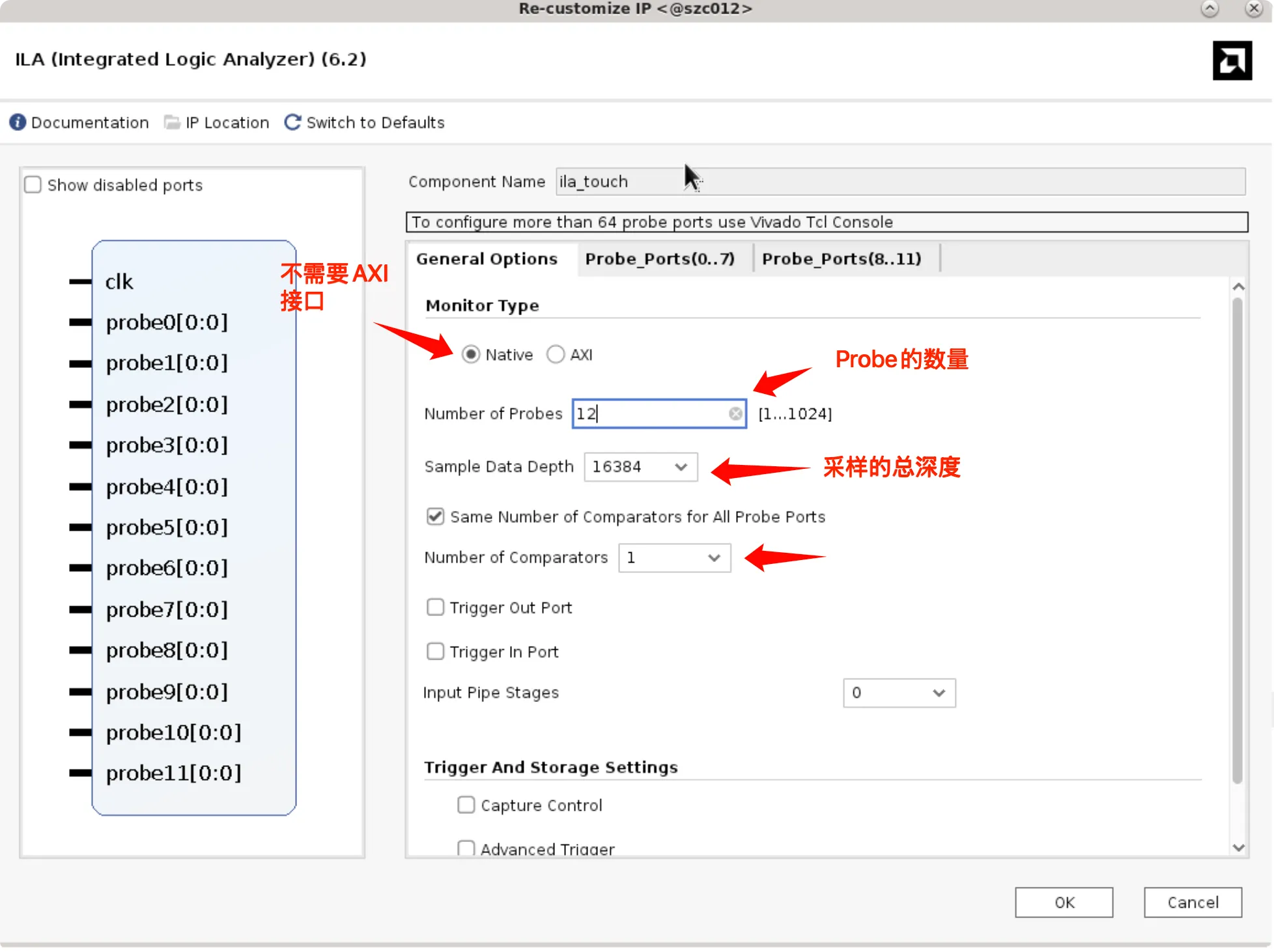

ILA 的基本组成

一个典型 ILA 包含:

- 采样时钟(clk)— 时钟信号应尽量采用芯片内部持续存在的时钟,这样可以确保 ILA能够正确的运行,否则可能出现时钟过慢点错误提示

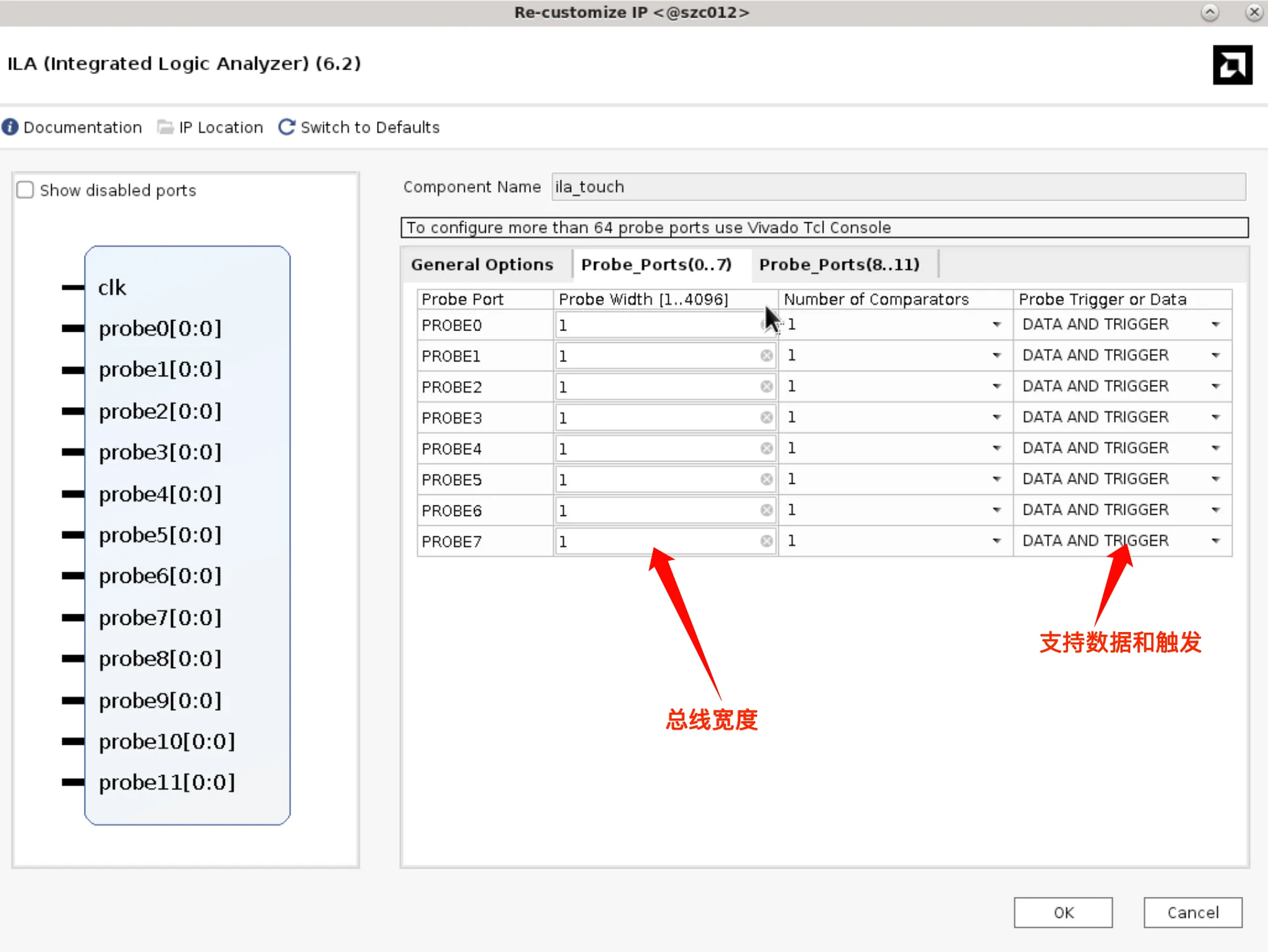

- Probe 信号(probe0…probeN)— 每一组Probe信号可以单独配置采样和触发逻辑,支持总线方式的显示,这个可以根据实际情况来配置。

- 触发逻辑 — 一般来讲简单的触发就可以满足大部分的调试场景。

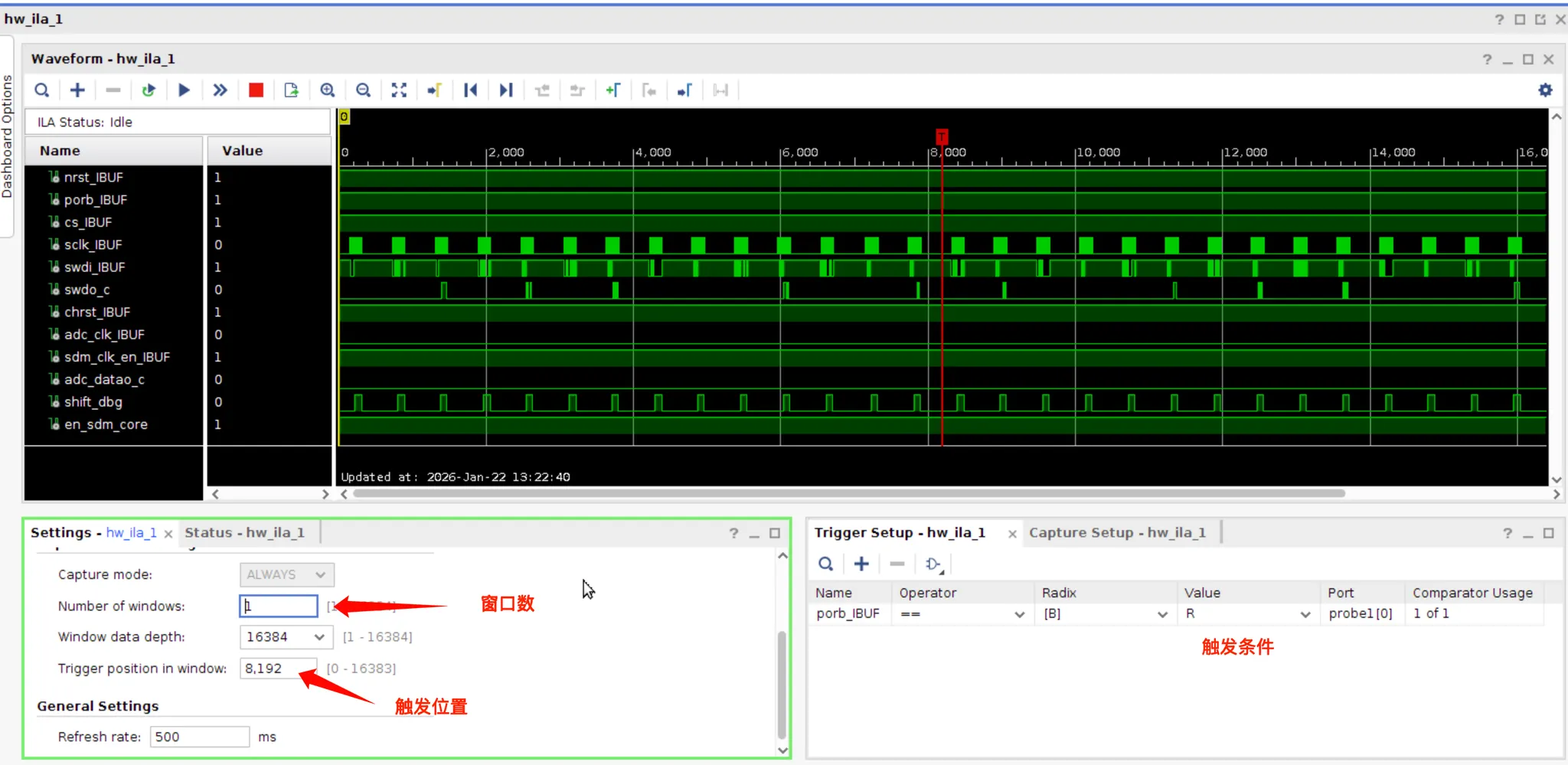

- 片内 BRAM 存储波形数据 — 这个主要取决于配置中要配置的采样长度,ILA其实也支持灵活的多段采集,这个可以根据实际应用需要进行配置。

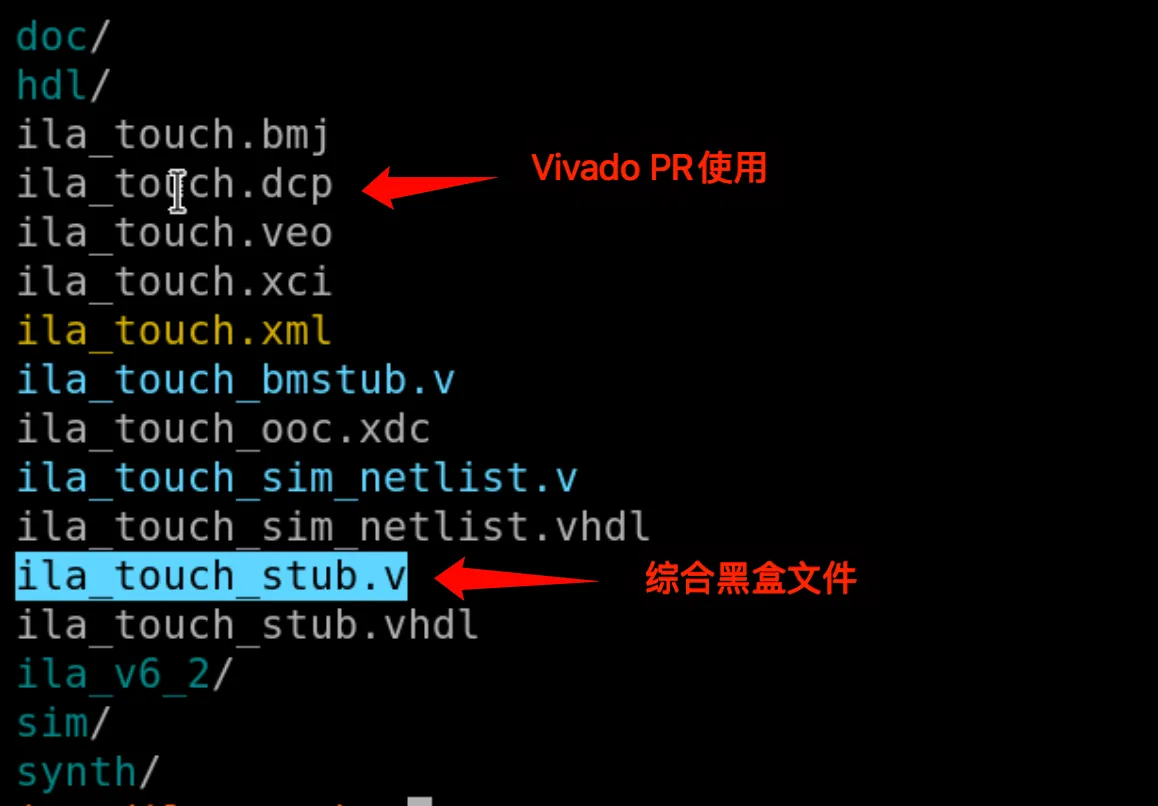

ILA生成文件

对于我的开发工作流来讲,对于ILA生成的文件主要有如下一些内容:

ILA集成到RTL中进行信号观测

生成好ILA IP之后我们就可以在我们的设计中加入生成好的IP,告诉工具采集哪些信号,这个过程可以直接在RTL中对生成好的IP进行例化,一个简单的例子如下:

(* syn_noprune = 1 *)

(* syn_preserve = 1 *)

ila_touch ila_dbg(

.clk(fpga_root_clk),

.probe0(reset),

.probe1(gobal_reset),

.probe2(select),

.probe3(sclk),

.probe4(swdi),

.probe5(swdo),

.probe6(module_reset),

.probe7(per_clk),

.probe8(per_clk_en),

.probe9(chip_data_out),

.probe10(debugA),

.probe11(debugB)

);上面就是一个典型的例化例子,我们只需要将对应的时钟和需要观测的信号连接到这个IP就可以了,另外例化开头的(* syn_noprune = 1 *)和(* syn_preserve = 1 *)是必须的,这样可以避免ILA的IP被Synplify工具优化掉。

综合的工程源文件应该加入对应的Stub.v

add_file -verilog "$PRJ_ROOT/rtl/ila_touch_stub.v"Vivado PR工程加入DCP

在PR阶段,我们通过Stub.v告诉综合工具对应的ILA 是一个黑盒,但是到了Vivado的PR阶段,我们必须要将对应的ILA IP加入工程来让Vivado知道如何链接对应的IP,这个可以通过在Vivado脚本中增加如下的内容来实现:

#### read dcp files #############

add_files -norecurse "ila_touch.dcp"注意dcp会有版本问题,高版本vivado生成的dcp文件在低版本是无法直接使用的,应该尽量保持版本一致。

开启调试文件生成

write_debug_probe -force ${DesignName}.ltx调试文件是用来在vivado lab中调试使用的,可以显示用户友好的信号名(PR后的信号名),虽然会包含一定的后缀,但是基本是可读的。

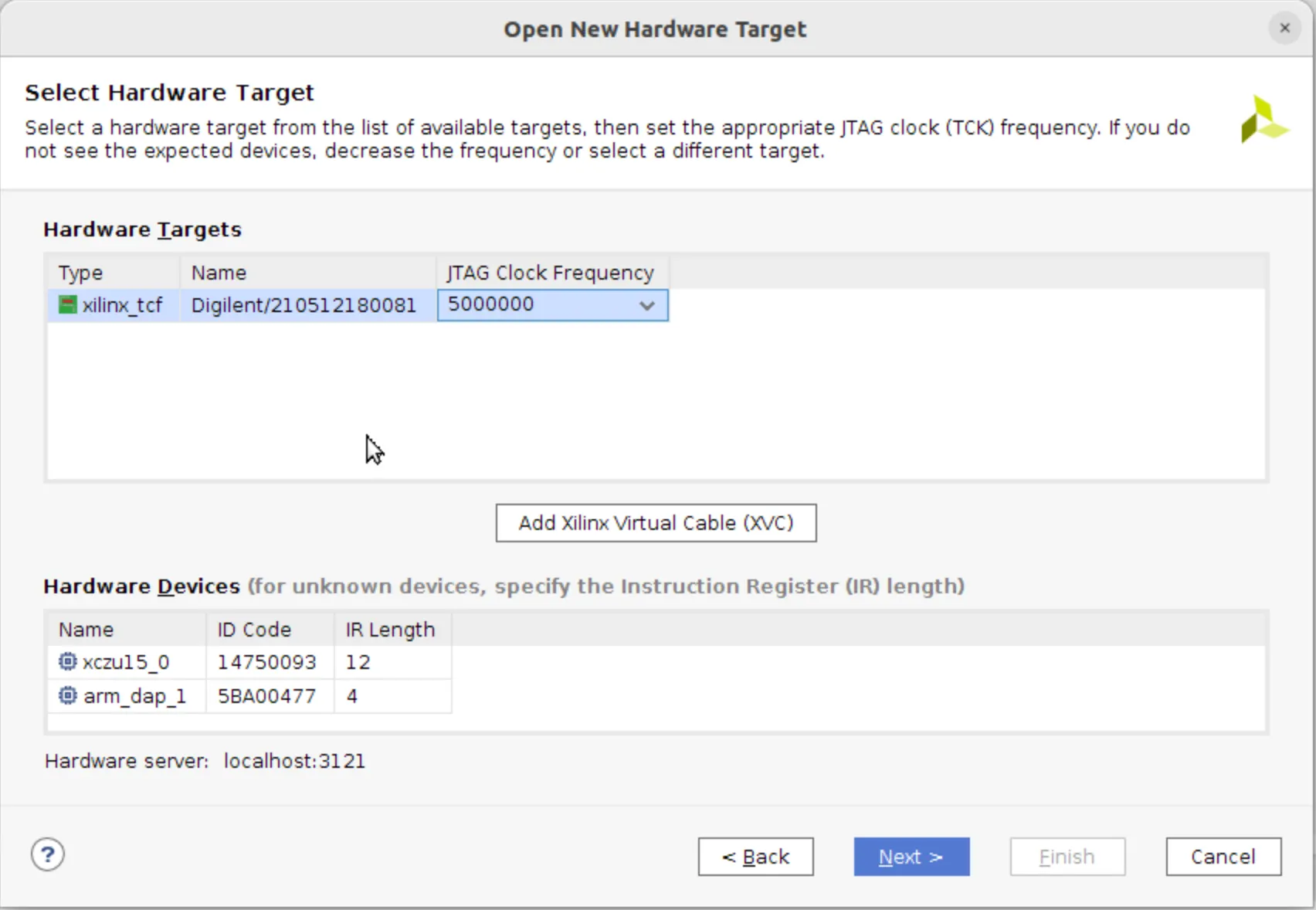

Vivado Lab配置注意事项

生成好对应的bit和ltx文件后,在Vivado Lab中也可以看到ILA,但是触发之后发现无法正常采样,这个可能是JTAG速率配置的问题,这个地方我卡了很久才发现这个坑。

经过如上的配置 ILA应该就可以正常使用了。

最后更新于 2026-01-24 00:22:26 并被添加「调试 FPGA 分析」标签,已有 1165 位童鞋阅读过。

本作品采用知识共享署名-非商业性使用-禁止演绎 4.0 国际许可协议进行许可。