UVM学习笔记(1)

UVM是现在比较流行的一种验证平台,所谓打验证平台一般要实现以下一些功能:

- 模拟DUT的各种真实的使用情况,也就是要给DUT添加各种激励,包括正常和异常的激励,UVM中激励是通过driver来实现的。

- 验证平台需要根据DUT的输出来判断DUT的行为是否符合预期,这个是通过记分板scoreboard (checker)实现的,当然这里面就有拿什么来判断,怎么个判断标准。

- 收集DUT的输出传递给scoreboard,完成这个功能的是monitor

- 给出正确的预期结果,这个是通过scoreboard完成的,在完成这个操作的时候一方面要求DUT进行运算,另一方面要求验证平台也做相应的运算,然后将两个结果送到scoreboard比较,所以就要求验证平台有一个参考模型(reference model)

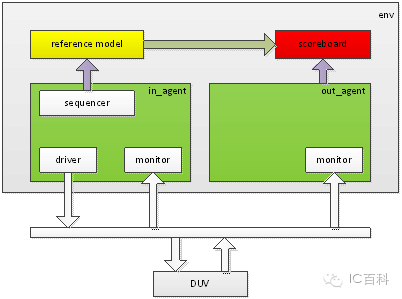

系统典型框图

上图是一个典型的UVM验证平台框图,可以看到这里的monitor分为两个,一个在输入部分,一个在输出部分,相对于DUT而言还有一个reference model,这里所有的driver, monitor, reference model socreboard等都是通过类来实现的,类是SystemVerilog的一个重要特点,也是其他编程语言中常用的一种编程模型,是面向对象的精髓所在。

在SystemVerilog中,类可以有函数(function)和任务(task),比如通过函数和任务我们可以实现driver的输出激励也可以完成monitor的监测功能以及scoreboard的比较功能,类还可以有成员变量,用于保存类的一些信息控制类的行为等等。在UVM中,当要实现一个功能的时候,首先要考虑从UVM已经存在的某个类派生出一个新的类,也就是UVM的一个基本原则:验证平台中所有的组建都应该派生自UVM中的类。

UVM中的类

派生自uvm_driver类的子类的new方法都有两个参数,一个是string类的name,一个是uvm_component类型的parent。这两个参数是uvm_componment要求的,这也是uvm_componment的一个基本特征。

driver所作的事情基本都是在main_phase中完成的,UVM通过phase来管理验证平台main_phase是uvm_driver中预定义的一个任务,可以简单的认为实现一个driver就相当于实现一个main_phase。

uvm_info是一个类似于display的一个宏定义,他的第一个参数是要打印的信息归类,第二个参数是具体要打印的字符串,第三个参数是冗余级别,比如UVM_LOW,注意UVM_LOW是非常关键的信息,而UVM_HIGH则是一个可有可无的信息的级别。另外还有uvm_error和uvm_warning

类的实例化是通过new关键字实现的。

工厂模式

现在看来这个UVM真的就是面向对象的实现呀,工厂模式都有,但是不知道这个工厂模式和面向对象里面的工厂模式是不是一样的。在UVM中,factory机制是通过uvm_component_utils宏定义实现的,这个宏可以将我们定义的类登记在UVM内部的一张表中,只要在定义类的时候使用这个宏,这个类就会被添加到这个表。在UVM中,所有派生自uvm_component类及其派生类的新类定义都要使用uvm_component_util进行类的注册。

Objection机制

在UVM main phase一般都要先调用raise_objection在结束的时候调用drop_objection,它们两个总是成对出现。

Virtual Interface

这又变成JAVA了,还有接口,看来真的挺全面,引入virtual interface主要是为了可移植方面考虑的。这块有点麻烦,后面慢慢展开。

Build phase

在UVM中,类似于main_phase,还有一个build_phase,他也是一个内建的phase,在UVM启动后会自动执行,并且是在main_phase之前执行,它主要通过config_db的get和set操作传递一些数据和成员变量,子类必须显式的调用父类的build_phase, build_phase本身不会占用仿真时间,并且总是在仿真时间为0的时刻调用。

好了,理论就先写着么多,先搞搞代码看看。

最后更新于 2018-12-23 00:07:20 并被添加「UVM」标签,已有 5836 位童鞋阅读过。

本作品采用知识共享署名-非商业性使用-禁止演绎 4.0 国际许可协议进行许可。