OV5640摄像头的时钟配置

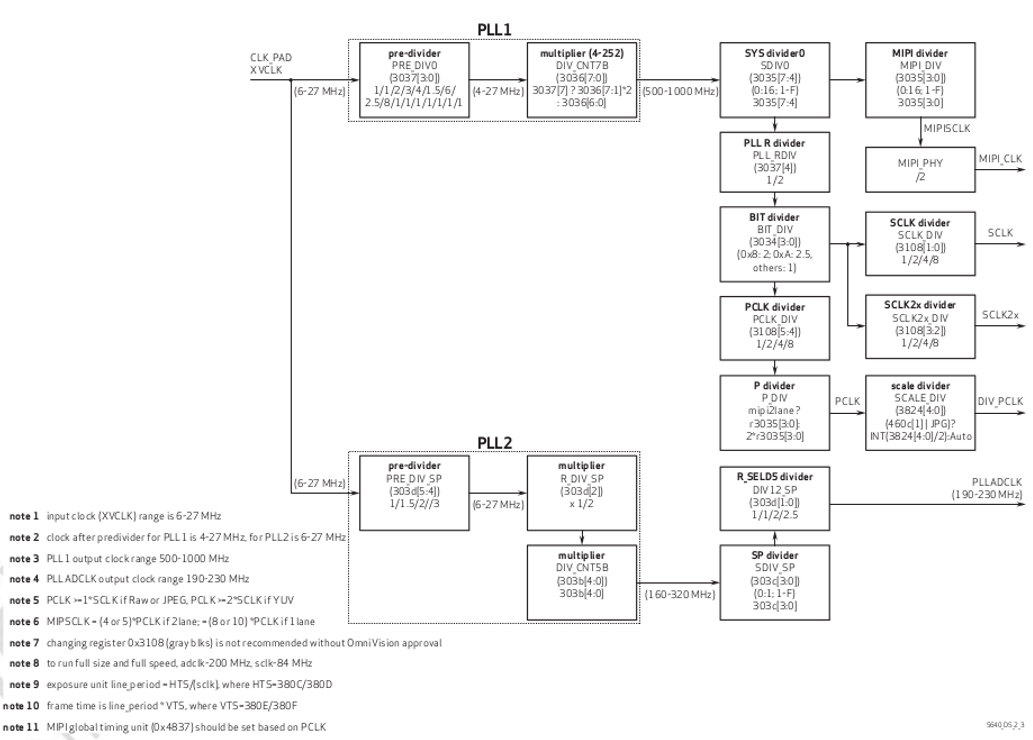

豪威半导体的数据手册似乎写的也是非常不靠谱,因为测试需要,我需要修改摄像头输出的MIPI时钟,网上下载的参考代码不能涵盖我的需求。本来想着看看手册就可以自己配置出来,但是看了之后发现里面完全没有PLL设置相关的资料,网上找了很久才找到一个不知道哪里来的框图:

这个框图看起来还是比较清晰的,但是里面具体寄存器的分频配置什么的就比较难懂了,这里就把基本关键的寄存器列举一下:

| Address | Name | Description |

|---|---|---|

| 0x3035 | SC PLL Control1 | Bit[7:4] System clock divider Bit[3:0] MIPI divider |

| 0x3036 | SC PLL Control2 | PLL multiplier(4~252) |

| 0x3037 | SC PLL Control3 | Bit[4] bypass/divided by 2, Bit[3:0] pre-divider |

举例分析

比如我们设置为720P的输出模式,这种模式下像素配置是740*1892=1400080*30=42002400*4=168009600,这里一大串算式,实际上是算了一个摄像头数据传输的码率,这里我们对这个公式进行一个分解。

首先,例子采用的是720P的图像模式,帧率是30帧,我们知道图像实际传输的时候分辨率会比我们用到的有效分辨率高,比如我们这里720P传输的时候并不是1280720,而是1892740,这样算下来每一帧图像总共有42002400个像素,图像帧率是30帧,这样每秒钟就有42002400*30=42002400个像素需要传输,假如每个像素有两个Byte,也就是16bit,这样每秒钟就是42002400*16=672038400个比特,而我们是两个通道传输,又是DDR模式,所以相应的时钟还要除以通道数目,再除以2(DDR模式),所以最终的时钟速率是168009600, 也就是168MHz。

现在我们根据这个来验证我们已知的PLL配置,首先我们看相应的寄存器配置如下:

| Register | Name | Value | Description |

|---|---|---|---|

| 0x3035 | PLL Control1 | 0x21 | System clock divided by 2, MIPI divided by 2 |

| 0x3036 | PLL Control2 | 0x54 | PLL multiplier by 0x54 = 84 |

| 0x3037 | PLL Control3 | 0x13 | PLL predivider is 31 |

这样我们根据实际参考时钟为24M来计算,首先24M经过3分频变为8M,然后经过84倍的倍频变为672M,在经过系统分频2变为336MHz,之后是MIPI的2分频,最终变为168MHz,和我们期望的频率一致。

好了,就这样吧,总算是把这个频率理得有点清楚了。

- 这里分频配置有点特别,不同值对应的分频分别是1,1,2,3,4,5,6,好吧,其实只是0对应1分频而已。 ↩

最后更新于 2019-07-24 05:57:23 并被添加「」标签,已有 19768 位童鞋阅读过。

本作品采用知识共享署名-非商业性使用-禁止演绎 4.0 国际许可协议进行许可。

请问是怎么知道720P下的像素配置是740*1892的呢?还有请教一下,MCU那边MIPI的配置是不是要和OV5640这边的MIPI_CLK匹配呢?

我人晕了 谁告诉你算时钟频率要乘BIT数的?lcd显示屏的行同步周期内,每个时钟单位是像素,也就是像素点扫描频率。