FPGA中Gate clock的处理

今天我们来看看FPGA porting时候对ASIC中Clock Gate的处理。我们知道ASIC设计中为了功耗考虑,常常会有大量的Clock Gate。而对这样的ASIC做FPGA验证的时候,这些Gate Clock会成为一个很大的障碍,因为FPGA中并没有这么多Clock Gate,并且Clock Gate会极大的影响FPGA设计的时序。因此,为了更好的实现FPGA的porting,我们来看看FPGA中对Clock Gate可以做哪些处理。

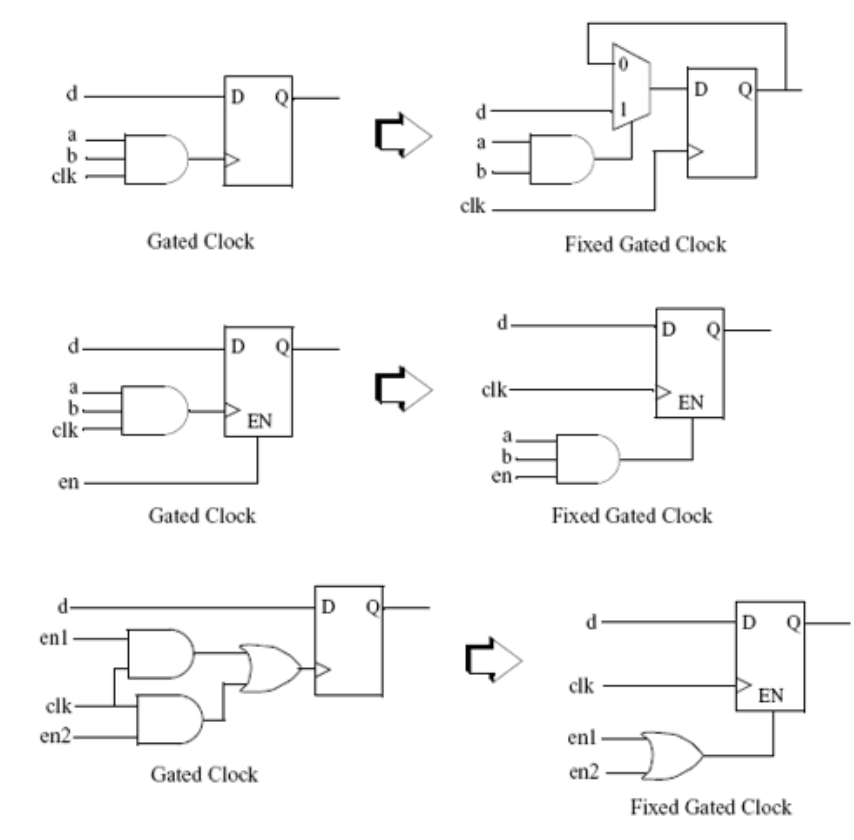

一般来说,Clock Gate就是clock和一个信号进行逻辑与操作,这样控制信号为低的时候,clock就不会继续输出,clock也就被Gate住了,这就是Clock Gate的简单实现。如果Gate Clock驱动一个寄存器,那么当clock停住之后,寄存器状态就不会变化。这个时候实际我们可以将寄存器的输出信号反馈到输入,这样就可以模拟一个不再变化的寄存器,也就实现了Gate Clock的转换。另外,如果寄存器有使能位的话,我们可以直接将Clock的使能信号和寄存器的使能信号相与,然后作为新的使能信号,这样也可以实现Gate Clock的转换。

其实这种转换很多综合工具已经可以支持了,比如Synplify Pro和Synplify Premier都可以实现这样的之中转换。不过工具中就是工具,在实际进行转换的时候,很多情况会影响工具的判断,比如:

- 相应的时钟有没有正确的定义

- 时钟转换的选项有没有正确开启

- 时钟结构中有没有使用原语或特殊cell

- 时钟结构中有没有MUX或者XOR逻辑(MUX和XOR逻辑只有HAPS中的Synplify Premier支持)

- 时钟逻辑中有其它影响转化的逻辑

- 是不是本身就是不支持的时钟结构

为了实现准确的时钟转化,一般要满足以下几个条件

- 派生出来的门控时钟必须是组合逻辑的输出。如果派生时钟是寄存器的输出是不能正常转化的。

- 组合逻辑中只有一个可以正常识别的基础时钟(其它信号不能是时钟),为了定义一个时钟网络,可以为时钟定义一个周期或者频率信息,比如

create_clock -name {clk} -freq 10.000 -clockgroup default_clkgroup - 使用工具支持的原语,如果用到了Black-box模块,那么需要在Black-box模块正确定义时钟输入和时钟使能信号

- 使用正确的Logic格式

所谓的正确Logic格式一般是满足下面两个条件:

- 对于所有的门控信号,至少有一个逻辑组合,这个逻辑组合要满足输入的基准时钟变化的时候,派生时钟不变化,也就是真的可以产生门控时钟

- 对于至少一个门控时钟的状态(高电平或者低电平),门控信号的变化不应导致派生时钟产生变化,其实就是不要有其他逻辑

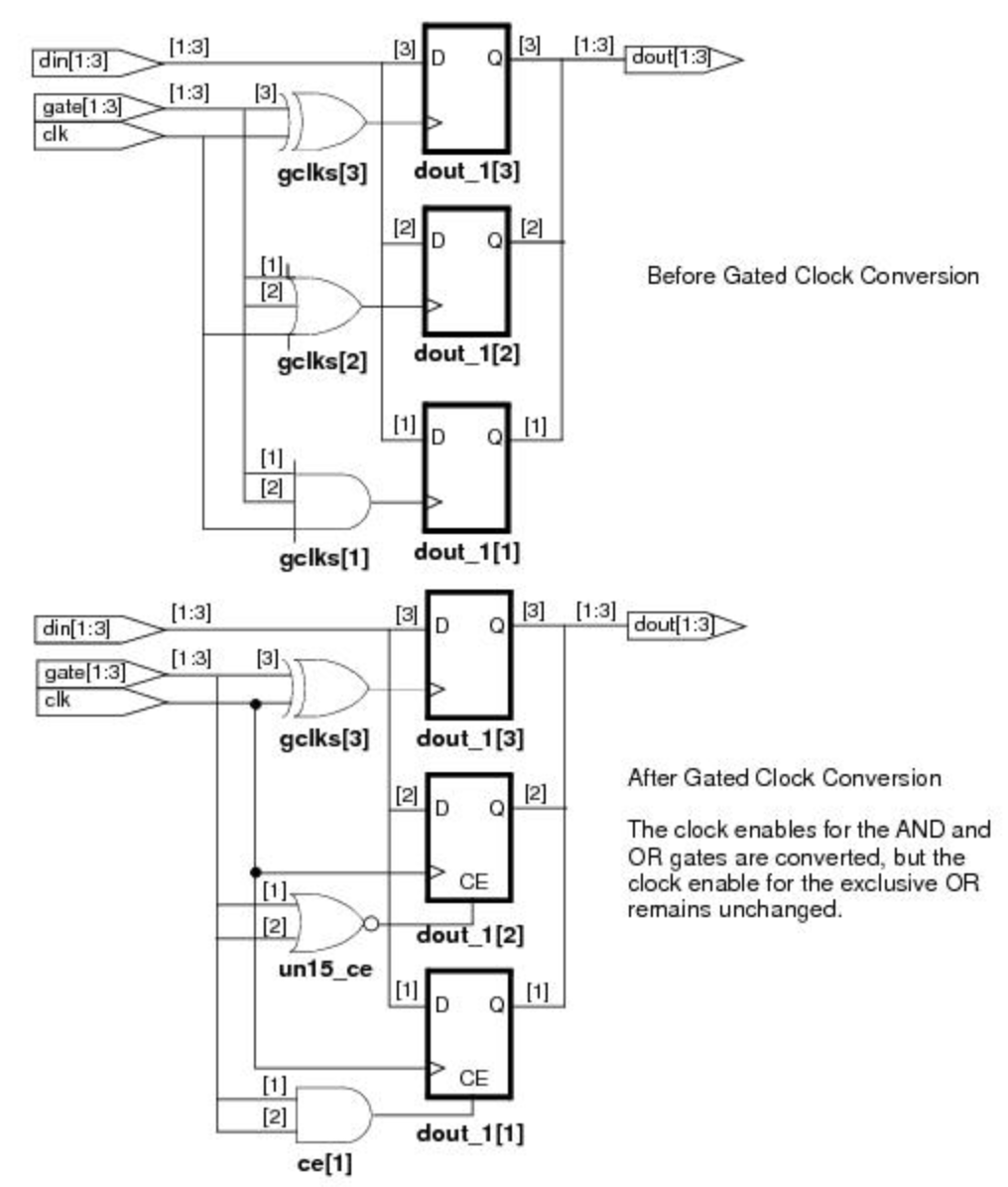

比如上图中就是一个无法转化和两个正确转换的例子。能正确转化的两个就先不说了,对于gclk[3]实际是三个控制信号和一个时钟做异或运算的结果,这个是无法正确转换的,因为时钟本身是异或的一个输入,无论时钟是高电平还是低电平,其它信号的变化都有可能使输出产生变化,也就是说即使没有时钟,这个逻辑也能产生一个派生时钟,这种情况工具是搞不定的。

对时钟信号的定义也是门控时钟正确转换的关键:

- 门控时钟的定义需要在后续后续逻辑的时钟输入端定义

- 通过create_generated_clock约束定义生成时钟和基准时钟的关系

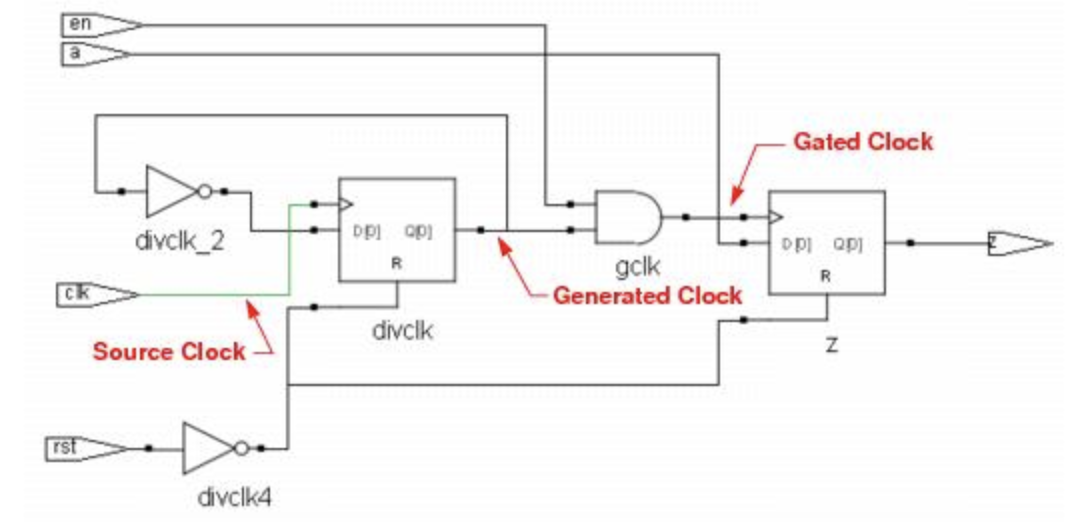

- 如果时钟逻辑中既包含门控逻辑和时钟生成电路,那么必须定义

create_generated_clock约束,没有这个约束,工具将无法判断门控信号和源时钟的关系

源时钟的定义:create_clock –name clk [get_ports clk] –period 10

生成时钟定义:create_generated_clock –name divclk [get_nets {divclk}] –source [get_ports clk] –divide_by 2

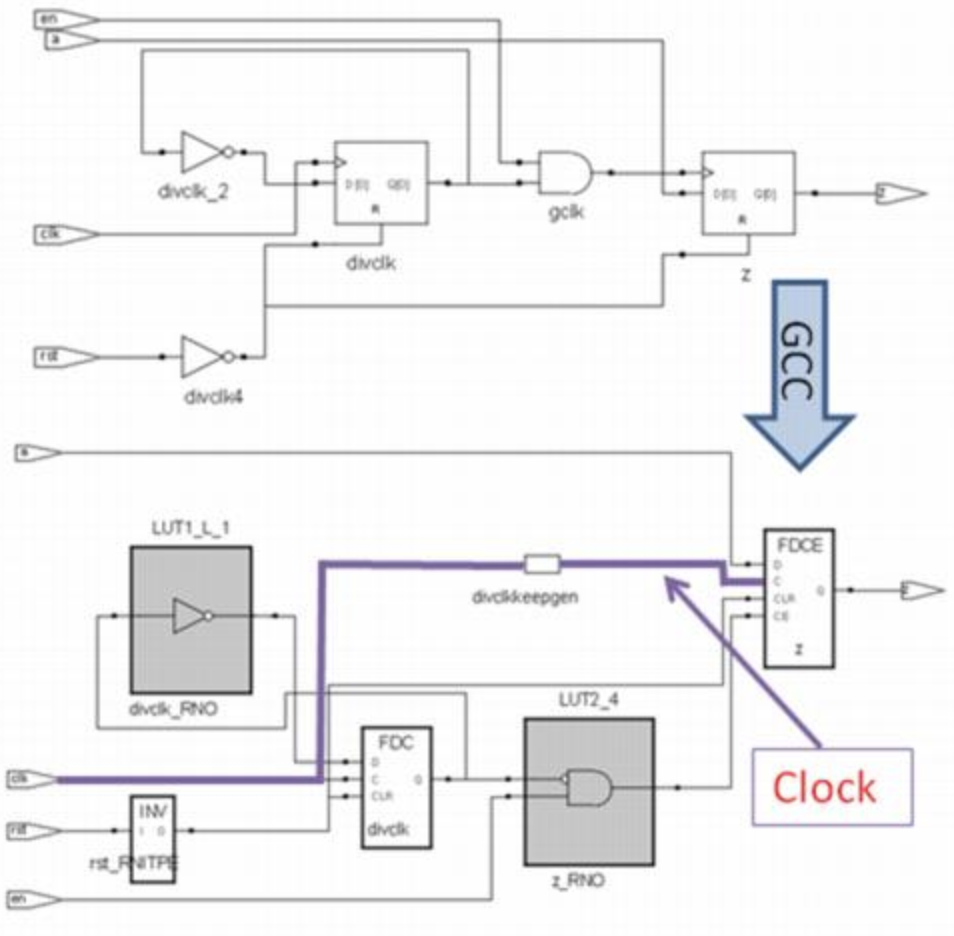

下图就是一个正确定义并正确转换的例子:

好了,困了,先说这么多,对了内容是从SolveNet上拿到的。

最后更新于 2019-11-27 13:51:09 并被添加「FPGA Clock」标签,已有 13382 位童鞋阅读过。

本作品采用知识共享署名-非商业性使用-禁止演绎 4.0 国际许可协议进行许可。