Zebu学习笔记(1)- 系统介绍

Zebu Synopsys公司推出的高容量仿真系统,具有移植简单,调试方便等多种优点。

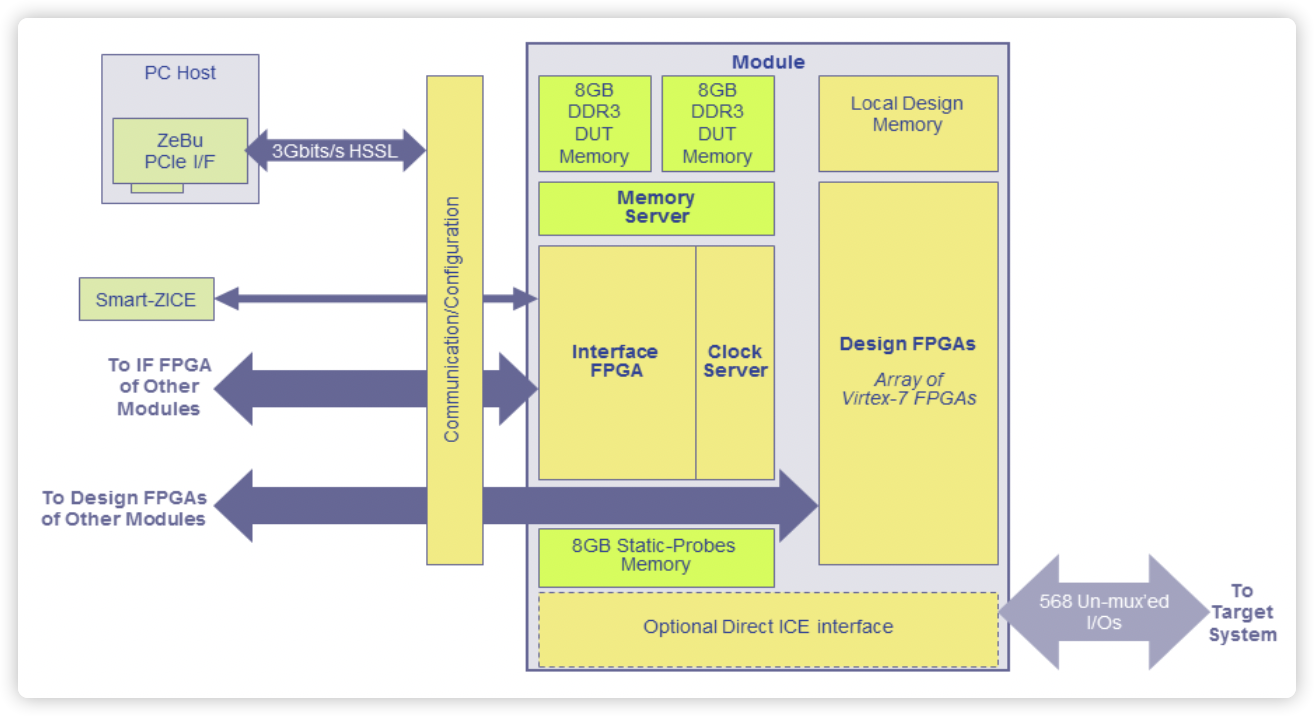

Zebu支持多种软硬件结合的调试方式,可以处理多数在Verification下具有挑战性的Bug调试,Zebu和通过PCI接口和PC通信,支持多个用户分Slot同时访问。另外Zebu还支持通过ICE(Direct In-Circuit Emulation)和Smart Z-ICE两种方式连接DUT,ICE可以提供类似FPGA引脚的物理接口,Z-ICE则是提供标准的JTAG接口,可以方便的用于软件调试。

Zebu Server 3内部集成多块Virtex-7 LX2000 FPGA, 具体的系统框图如下:

Zebu仿真的基本流程

在Zebu仿真系统中,RTL设计文件和工程相关的文件都是通过VCS管理和编译的,Zebu的工程文件是一个Unified Compile Zebu文件(UTF),该文件包含编译的相关参数和配置,Zebu的编译是通过zCui完成的,该工具可以在命令行或者GUI模式下运行。

编译过程主要产生如下的文件:

- FPGA运行的bit文件,这些文件运行时会直接下载到FPGA

- 运行时用到的数据,这部分数据主要供上位机使用

UTF文件简介

UTF文件包含了Zebu编译所需的所有内容,这个文件是一个tcl脚本,可以控制编译的具体流程。典型的UTF文件包含以下一些内容:

| Settings | Description | Requirement |

|---|---|---|

| VCS compile commands | 命令可以直接调用VCS,定义设计顶层名称,可以定义哪些模块不被综合 | 必须有 |

| HW configuration | 指定描述硬件结构的tcl脚本,这个脚本在Zebu安装时产生 | 必须有 |

| Front-end compilation | 执行memory生成和指定黑盒(black box) | 可选 |

| Back-end compilation | 定义集群相关参数和时钟处理方法 | 可选 |

| zCui compilation | 定义远程运行命令和并行编译的任务数目 | 可选 |

| Debug options | 提供Combination Signals Accessibility(CSA)和运行后的调试信息 | 可选 |

对于VCS的utf命令,我们可以通过如下的命令获取相应的帮助信息

vcs -help utf+all: 显示所有的命令vcs -help utf+<command>: 显示<command>对应的帮助vcs -help utf+\*:显示所有命令的详细帮助信息

比如我们可以用vcs -help utf+\* > help.txt保存所有命令的帮助信息,可以方便查阅。

最后更新于 2020-02-27 07:02:39 并被添加「仿真 FPGA Zebu EDA」标签,已有 32450 位童鞋阅读过。

本作品采用知识共享署名-非商业性使用-禁止演绎 4.0 国际许可协议进行许可。

你好,刚刚接触zebu,我尝试按照example,跑了一遍Basic_STB。这个基础的demo,用了一个FPGA。当前想学习下如何降分割流程加入进来,做个简单的demo,将逻辑分割到2个FPAG。看到手册中有讲述zManualPartitioner工具,但进到实际工程中一直没知道怎么去完成partition流程。您是否可以指导下该如何操作带partition的工程?谢谢