SAR ADC多通道采样电路设计注意事项

现在 MCU 中对于 ADC 通道的需求越来越高,而 MCU 受成本限制往往不会放多个 ADC 模块,普遍都是采用多个通道分时复用 ADC 转换核心的方式实现多通道的采样。

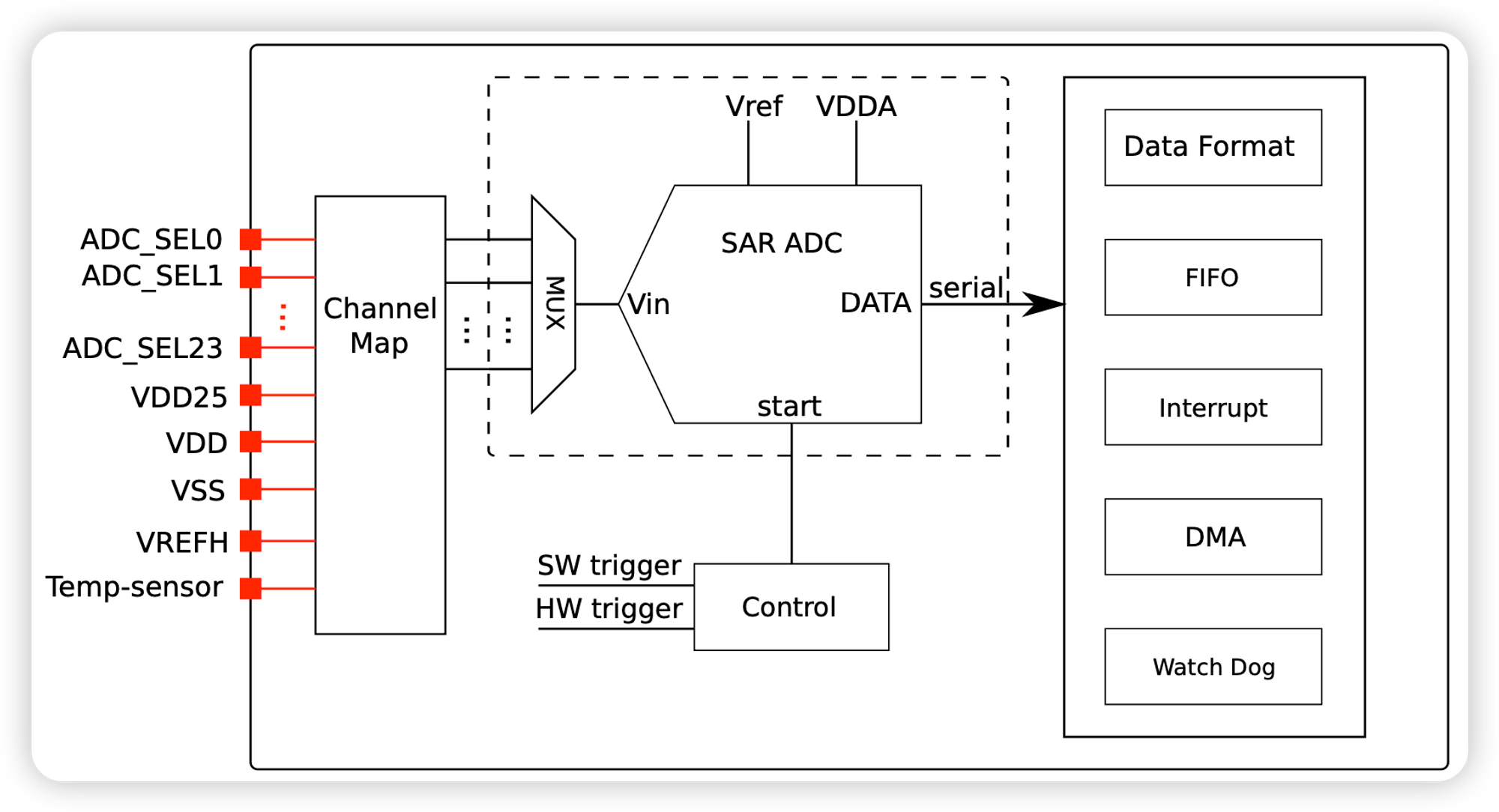

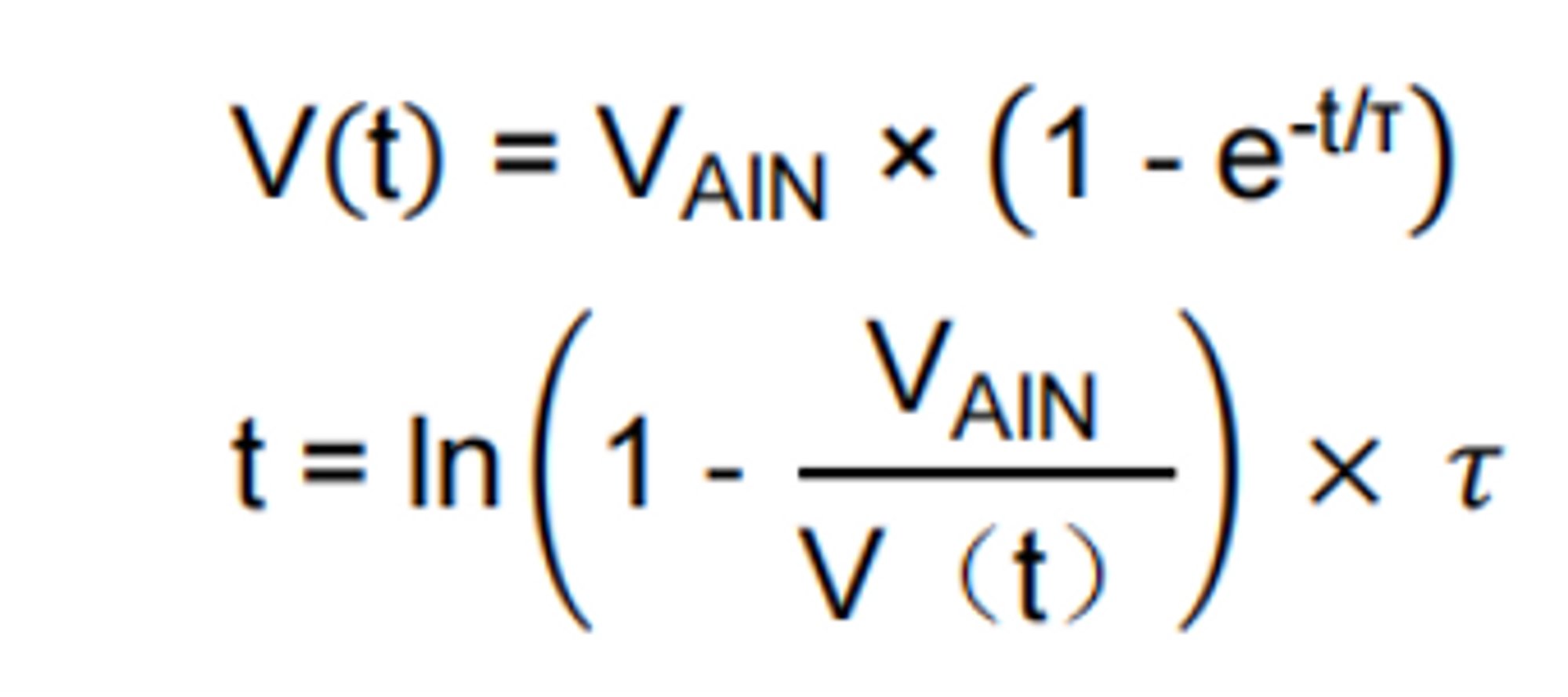

上图所示是云途 YTM32B1ME0 产品的 ADC 框图,可以看到 ADC 采用 SAR 结构的转换核心,核心外部通过一个 MUX 实现多个通道的选择。

对于 SAR 结构的 ADC,采样保持电路是一个非常重要的组成部分,一般都需要特殊设计,在 ADC 内部占用的面积也比较大,所以这个采样保持电路一般都是放在 MUX 之后,也是就是所有通道是共用一个采样保持电路。本篇文章讨论的 ADC 采样问题就是围绕这个采样保持电路展开的。

SAR ADC 基本原理

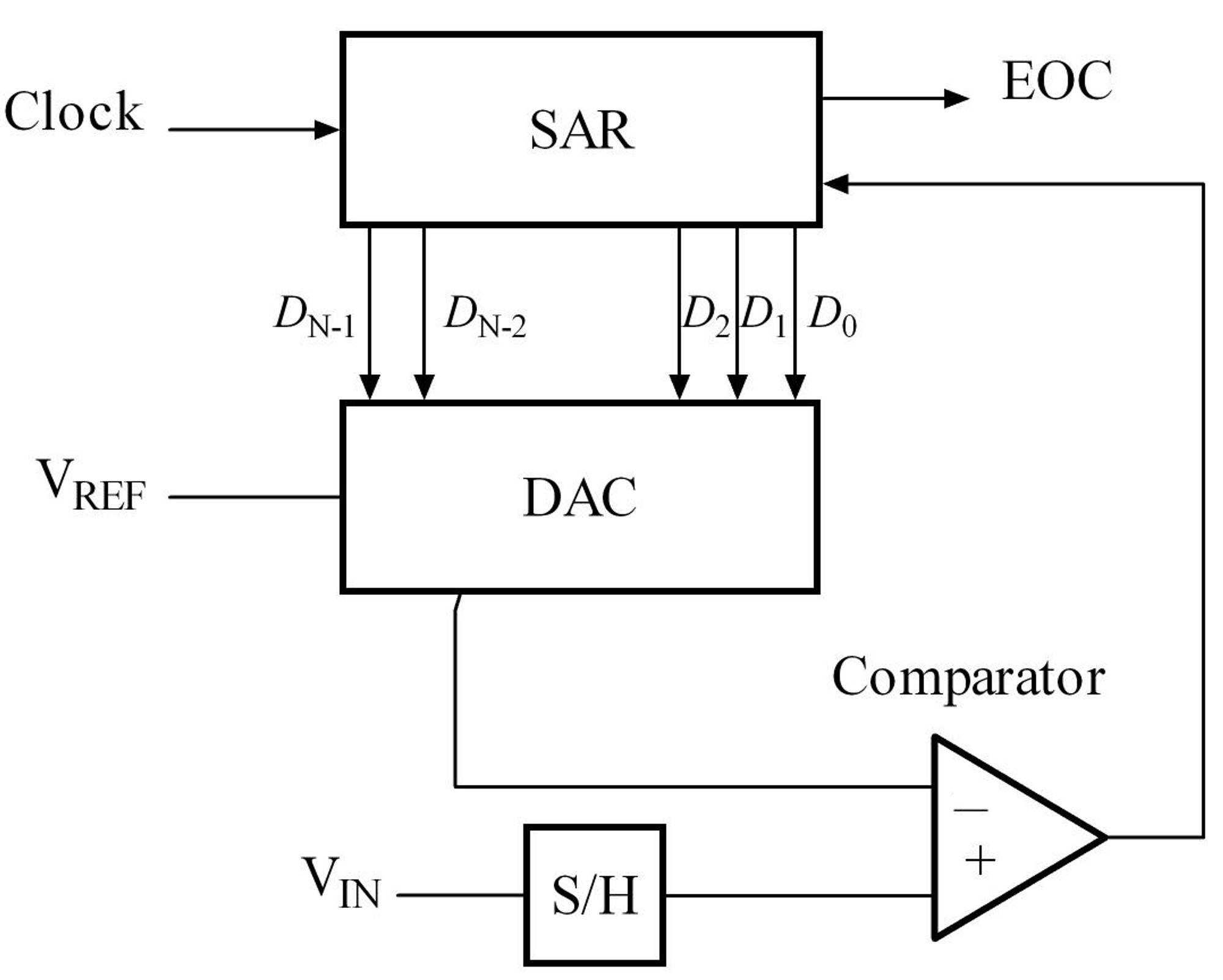

上图是 SAR 的基本结构,SAR ADC 内部有个 DAC,可以逐次产生一个比较电压,改电压和采样保持的电压依次比较,比较结果反馈调节 DAC 的输出,直到 DAC 的输出和输入相匹配,此时 DAC 的输入值就是 ADC 的转换结果。整个过程可以参考如下的图片:

采样保持电路

从上述 SAR ADC 的原理来看,ADC 的采样精度很大程度上取决于采样保持电路(S/H)的精度,采样保持电路对于外部输入而言可以简单等效为一个电容,这个电容的容值一般在 pF 级别,并不是很大。因为该电容容量过大则需要比较大的充电电流,采样保持电路的电压也需要比较长的时间才能和外部电压匹配,这个匹配时间我们称为采样建立时间。另外如果外部充电电流比较大,则可等效认为 ADC 的输入阻抗比较低,这个时候对于驱动能力比较弱的信号则可能出现电压下降的问题,最终造成采样不准确。

从上述对于采样保持电路的分析,我们可以的得出这么一个结论:如果需要比较高的输入阻抗,则采样保持电路的电容需要尽量小,但是电容太小又会影响 ADC 的转换。

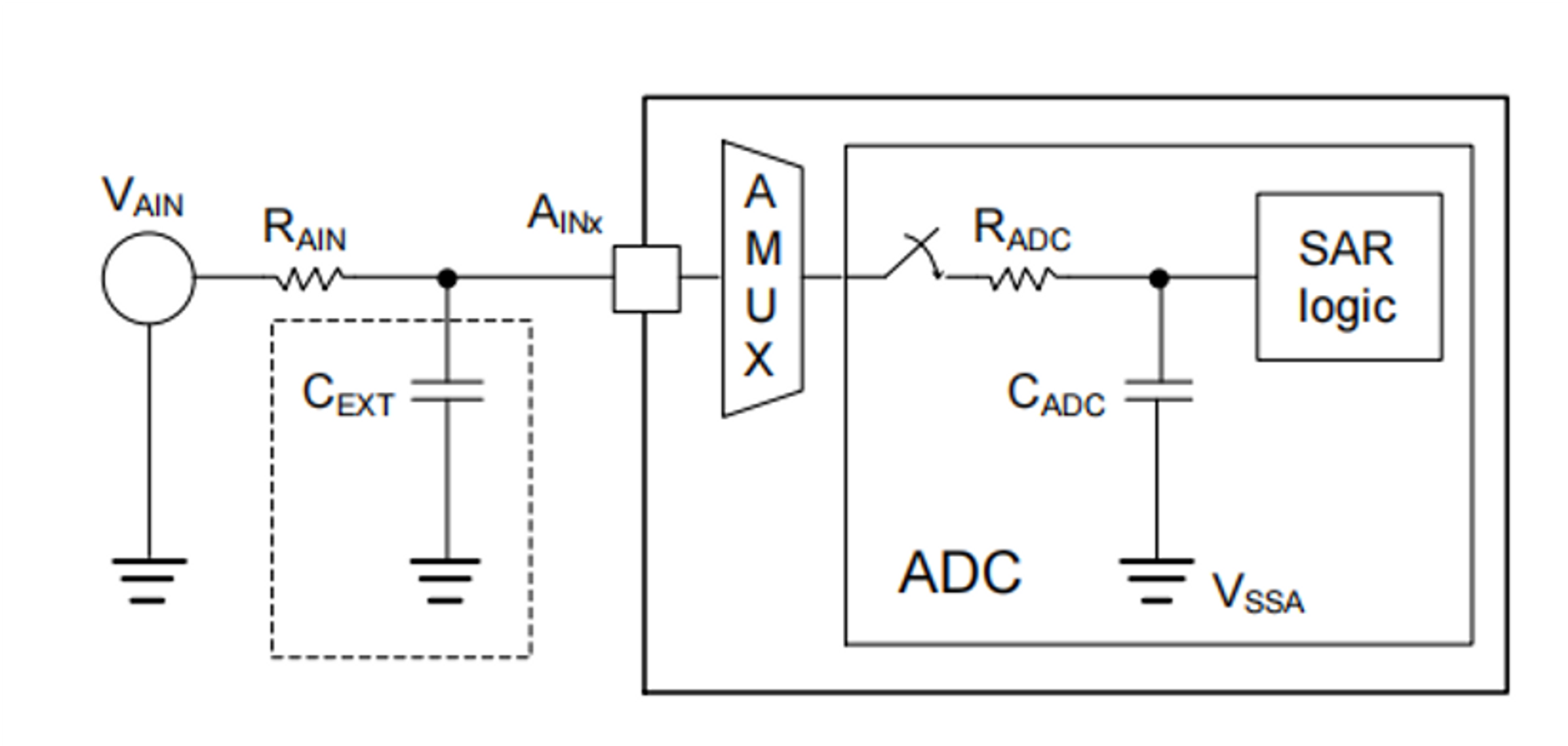

如图所示,其中模拟信号输入源对 ADC 的输入阻抗($R_{AIN}$),直接与 ADC 采样时间有关,影响 ADC 转换结果甚巨。未考虑输入阻抗使得 ADC 输入的外部器件与软件设置的采样时间不匹配,往往是造成 ADC 使用问题的原因。以下分别针对信号源具有一般输入阻抗(电压源驱动能力足够强)或高输入阻抗(电压源驱动能力不够强),分别探讨如何正确设置 ADC 的软硬件。

如果外部电压源驱动能力足够强(电压源内阻足够小),对于固定的采样时间,$C_{ADC}$ 电容需要在此固定时间内将电压建立到足够的精度,从 0V(假定之前转换完全放电)充电到 $V_{AIN}$ ,因此,$V_{AIN}=V_{REF}$ 是验证最大源电阻时要考虑的最坏情况。通过软件设置增加采样时间或降低 ADC 时钟频率可等效加长采样时间,当采样时间越长越可以获得好的转换结果。

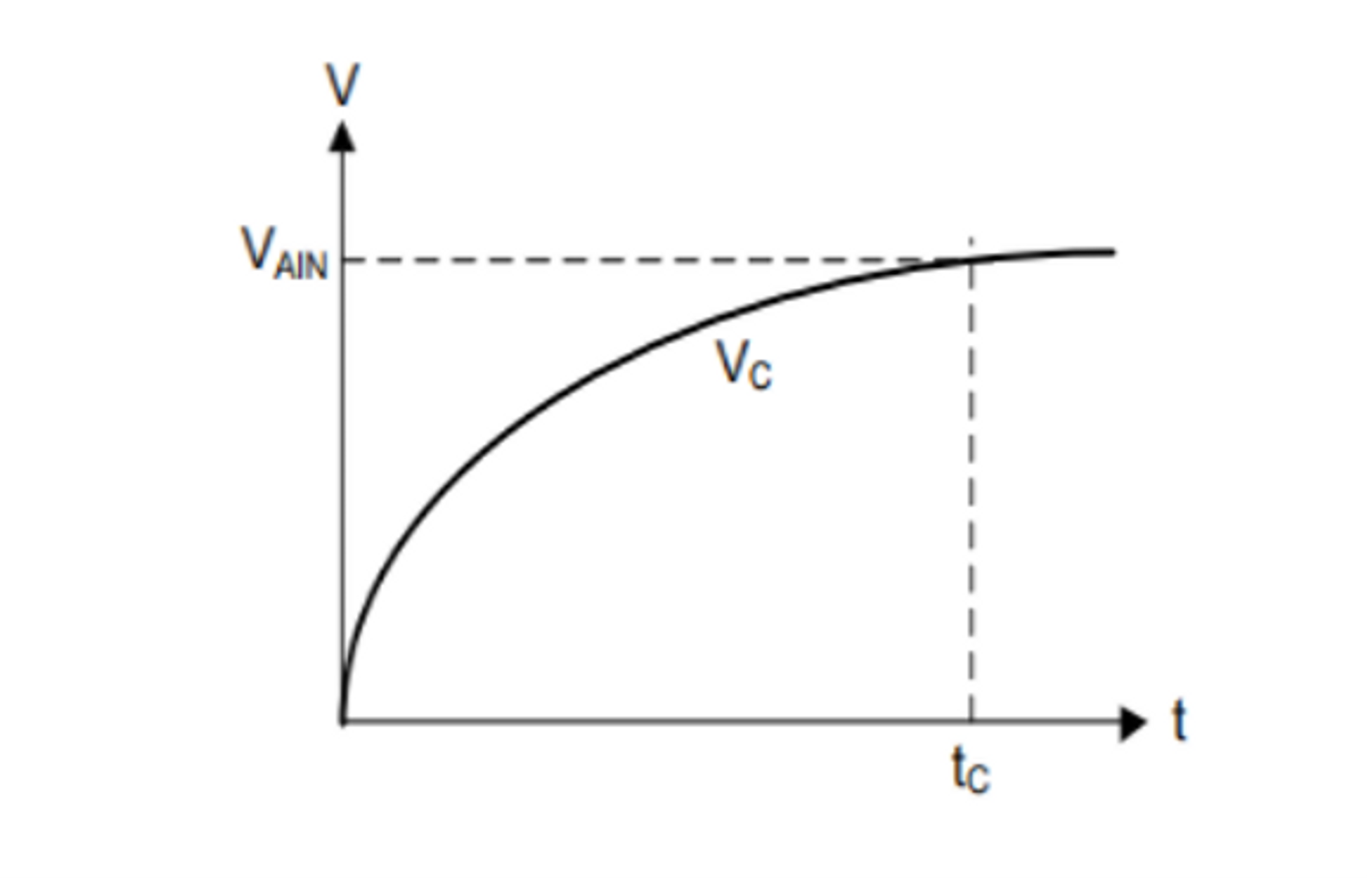

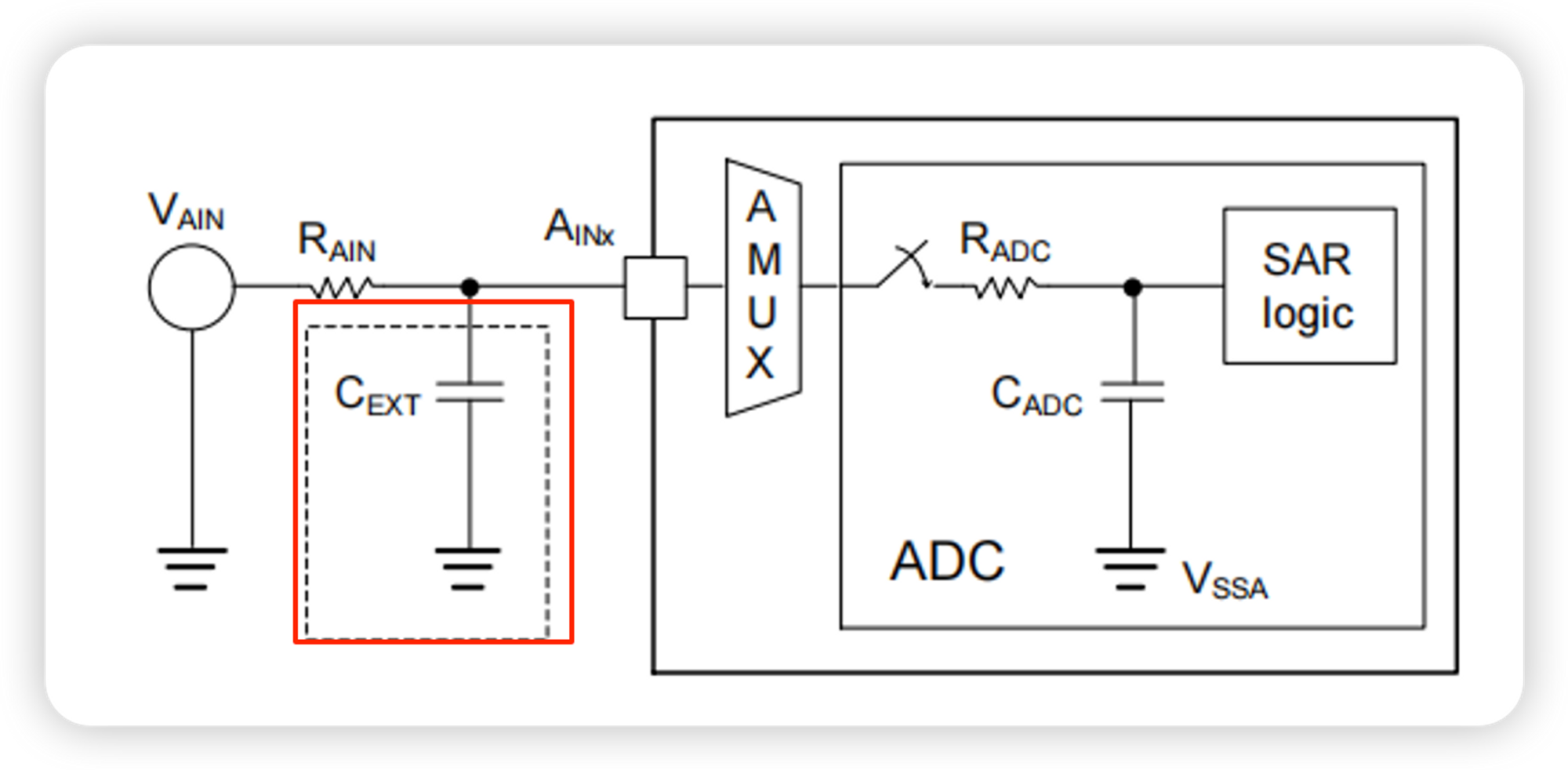

如上图所示,模拟信号源对采样保持电路充电,一般我们假设允许最大误差为 1LSB,按照 RC 充放电公式

按照 YTM32B1ME0 2MSPS 采样速率,采样时间 100ns 来计算:

$$ 8.32 * (R_{AIN} + R_{ADC}) * C_{ADC} < 100ns $$

按照 $C_{ADC} = 10pF$ 计算,则 $R_{AIN} + R_{ADC} < 1.2Kohm$

而实际 ADC 输入信号源常有存在高阻特性,例如系统电池电压分压后输入给 ADC 采集,因分压电阻会形成一个直流耗电路径,为了节省功耗,分压电阻常使用 100K 欧姆~1M 欧姆。这种硬件组合如若提高采样时间仍无法获得准确的采样结果,可以采用外接电容作为电荷存储器的方法来解决采样精度的问题,正常状态,外部电容总是可以保持外部输入电压,当需要转换的时候,此电容参与采样时电路的充放电过程,以便向 SAR ADC 的采样电容提供充足的电荷,而对内部电容快速充电,并且稳定 ADC 输入点的电压。

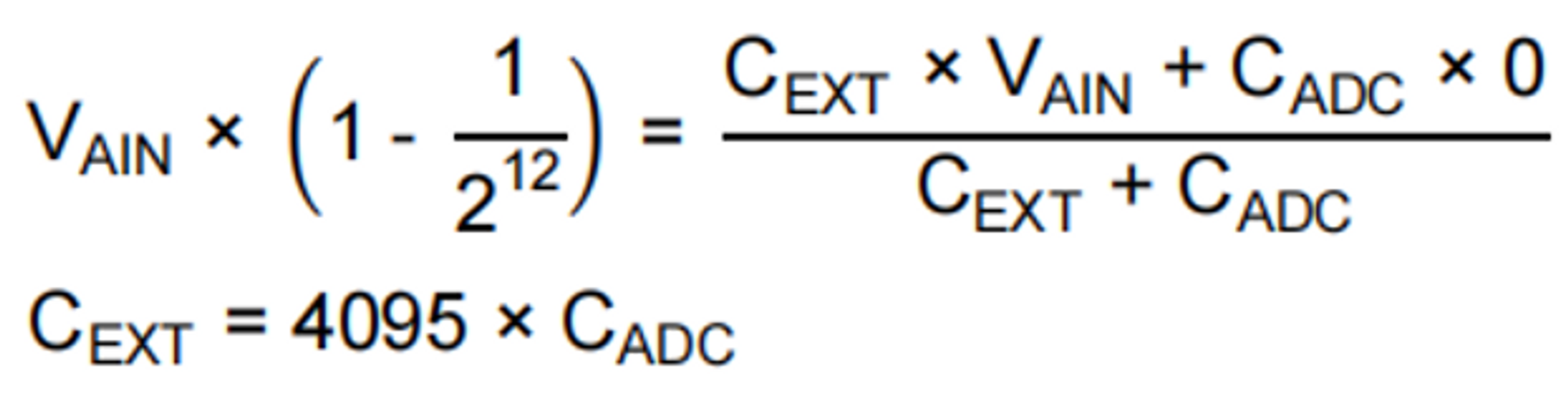

当采样开关接通后,会在 $C_{EXT}$ 和 $C_{ADC}$ 之间有一段电荷重新分配的过程,假设 $C_{ADC}$ 现在是完全放电的, $C_{EXT}$ 存储着和 $C_{AIN}$ 一样的电压,$V_C$(分配后的电压)定规为 $V_{AIN}$ 的 0.999939 倍,这个意义是 $V_C$ 最后徧差在 $V_{AIN}$ 的 1 LSB 之内,以 12 位解析度来

假如内部电容阵列的大小为 10pF,$C_{EXT}=4096\times10pF=41nF$,这是外部电容的绝对最小值,实际选择过程中,可适当选择大一点,但是过大会限制 ADC 的输入带宽。

如果 $C_{EXT}<4095\times C_{ADC}$,提高采样时间有助于提升采样精度。

总结

对于通道复用类型的 SAR 结构 ADC,需要搭配合理的外部电路实现对信号的精确采样,当然也可以直接使用增加采样时间的方式。对于两种方案的选用需要考虑实际的应用需求。

另外对于需要高速采集的信号,正确的采样也需要注意如下要求:

- 如果只是对单一信号进行采集,SAR 不需要切换通道,这个时候对 SH 的建立时间要求并不高,SH 可以快速的跟踪外部信号,一般也不需要特殊的外部电路

- 如果需要对多个信号进行高速的转换,那么需要外部信号源驱动能力比较强,或者增加外部电容(降低输入带宽)

最后更新于 2023-08-20 01:52:41 并被添加「」标签,已有 10651 位童鞋阅读过。

本作品采用知识共享署名-非商业性使用-禁止演绎 4.0 国际许可协议进行许可。